# **TDC3310**

# Video D/A Converter 10-Bit, 40 Msps

### **Features**

- 10-bit resolution

- Single +5 volt power supply operation

- DC to 40 Msps, guaranteed

- ±1.0 LSB linearity error

- TTL-compatible inputs

- 1 Vp-p video output

- Sync and Blank controls

- · Video invert control

- · Very low glitch energy

- · Very low cost

## **Applications**

- Reconstruction of composite video

- High-resolution video

- · Low-cost video systems

- Set-top RF converter boxes

- Satellite receivers

- Direct digital synthesis

- Multimedia

### **Description**

The TDC3310 is a very high-speed 10-bit D/A converter especially suited for low-cost video applications. The TDC3310 offers 10-bit resolution, TTL-compatible inputs, and requires only a single +5 volt power supply. It has a single-ended voltage output, SYNC and BLANKing control inputs and an INVERT input that reverses video levels without altering either SYNC or BLANKing.

Operating at data rates up to 40 Msps, the TDC3310 is ideal for reconstructing composite NTSC, PAL and RS-343A video waveforms. Data is decoded and registered ahead of the current switch array, resulting in outstanding low-glitch characteristics.

The TDC3310 is available in a 32-Lead Plastic J-Leaded PLCC and 28-pin plastic packages and is guaranteed from 0°C to 70°C.

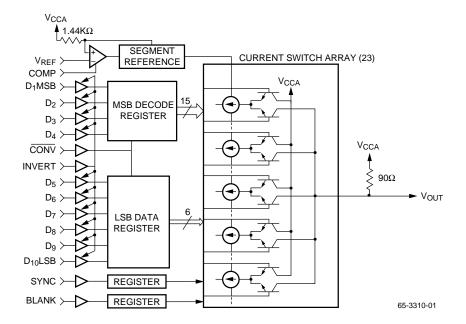

# **Block Diagram**

### **Functional Description**

The TDC3310 consists of five major circuit sections: the data and control registers, the MSB decode block, the MSB current switch array, the binary weighted LSB array and the reference amplifier. All inputs are registered just before the current switch array to minimize the temporal skew that generates glitches.

The TDC3310 uses an architecture that combines segmentation and binary weighted techniques. With the four MSBs segmented into 15 equal-value current switches, and the six LSBs using binary weighting, an optimal trade-off between glitch performance and die size (cost to the user) is made. The result is a very low cost, high performance D/A converter.

### **Power and Ground**

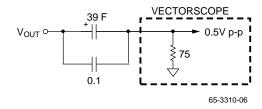

The TDC3310 requires a single +5.0 volt power supply. The analog (V<sub>CCA</sub>) and digital (V<sub>CCD</sub>) power supply voltages should be separately decoupled, as shown in Figure 8, to reduce power supply induced noise.  $0.1~\mu F$  decoupling capacitors should be placed as close as possible to the TDC3310 power pins. Ferrite beads are neither critical in value nor always required.

The high slew rate of digital data makes capacitive coupling to the outputs of any D/A converter a potential problem. Since the digital signals contain high frequency harmonics of the  $\overline{\text{CONV}}$  signal, as well as the video output signal, the result of data feedthrough often looks like harmonic distortion or reduced signal-to-noise performance, Separate analog and digital grounds are provided on the TDC3310, but all ground pins should be connected to a common solid ground plane for best performance.

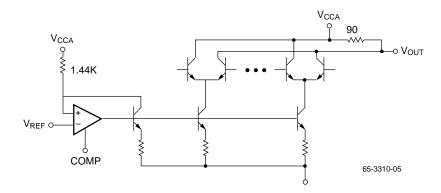

### **VREF**

The TDC3310 is designed to operate with a voltage reference referred to V<sub>CCA</sub> (a 1V difference between V<sub>REF</sub> and V<sub>CCA</sub>). The TDC3310 uses this voltage differential to generate an internal reference current for the current switch array. Since the DC voltage provided to V<sub>REF</sub> must be referred to V<sub>CCA</sub> (and not A<sub>GND</sub>), the output voltage of the D/A converter is referred to V<sub>CCA</sub> (and not to A<sub>GND</sub>). This allows the gain of the TDC3310 to be immune from variations of V<sub>CCA</sub>. V<sub>REF</sub> should be decoupled to V<sub>CCA</sub>.

The internal reference amplifier has a high-impedance input and is externally frequency-compensated to ensure stability. A  $0.1~\mu F$  capacitor should be connected between the COMP pin and AGND. The Typical Interface Circuits, shown in Figure 8, include an adjustable reference circuit.

### Data Inputs D<sub>1-10</sub>

The data inputs are TTL-compatible. For applications involving fewer than 10 bits, connect the unused LSBs to DGND.

### CONV

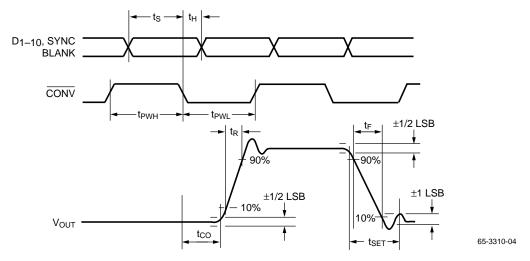

The TDC3310 requires a TTL-compatible clock signal,  $\overline{\text{CONV}}$ . All inputs are registered on and the analog output changes t<sub>CO</sub> after the falling edge of  $\overline{\text{CONV}}$ .

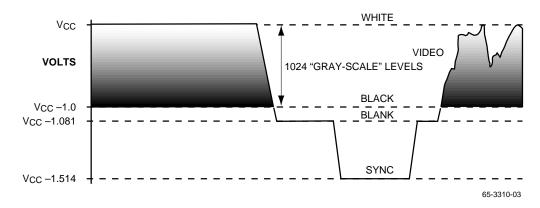

### SYNC and BLANK

SYNC and BLANK inputs control the output level of the TDC3310 during CRT retrace intervals. When BLANK is HIGH, data to  $D_{1-10}$  are ignored and  $V_{OUT}$  is forced to a fixed blanking level, nominally 81 mV below the video "black" level. When SYNC is HIGH, data to  $D_{1-10}$  and BLANK are ignored and  $V_{OUT}$  is forced to a fixed sync level, nominally 433mV below the level corresponding to BLANK. SYNC and BLANK are registered within the TDC3310 on the falling edge of  $\overline{CONV}$ .

#### INVERT

INVERT controls the polarity of  $D_{1-10}$  without affecting the SYNC or BLANK inputs. This input functions as a system data format selector, allowing the reversal of black and white in a video image. See the Input Coding Table. INVERT is registered within the TDC3310 on the falling edge of  $\overline{\text{CONV}}$ .

### Vout

The voltage output of the TDC3310 is referred to  $V_{CCA}$  and varies from  $V_{CCA}$  to  $V_{CCA}$ – $V_{REF}$ . The  $V_{OUT}$  terminal of the TDC3310 has an internal  $90\Omega$  resistor to provide a voltage output from the current switch array. The close thermal coupling and matched temperature coefficients of the internal reference current generator and this  $V_{OUT}$  load resistor provide an output that is stable over temperature. Operation with an external load resistor will reduce output voltage range as well as temperature stability. Current may be driven into or out of the  $V_{OUT}$  terminal as long as the output compliance voltage limit of the TDC3310 is not violated.

#### **Not Connected**

There are several pins with no internal connection to the TDC3310. They should be left open.

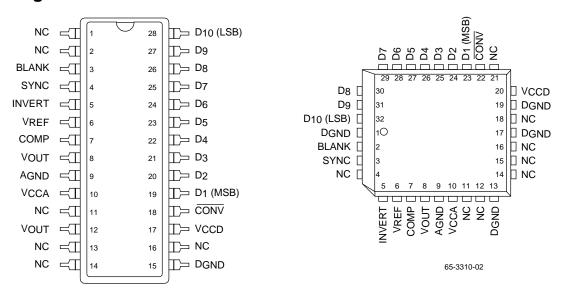

# **Pin Assignments**

# **Pin Descriptions**

|                       | Pin Nu                  | Pin Number                  |          |                                          |

|-----------------------|-------------------------|-----------------------------|----------|------------------------------------------|

| Pin Name              | PDIP                    | PLCC                        | Value    | Pin Function Description                 |

| Power                 |                         |                             | <b>!</b> |                                          |

| VCCA                  | 10                      | 10                          | 5.0V     | Analog supply voltage.                   |

| VCCD                  | 17                      | 20                          | 5.0V     | Digital supply voltage.                  |

| Ground                |                         |                             | '        |                                          |

| AGND                  | 9                       | 9                           | 0.0V     | Analog ground.                           |

| DGND                  | 12, 15                  | 1, 13, 17, 19               | 0.0V     | Digital ground.                          |

| Reference             |                         |                             |          |                                          |

| VREF                  | 6                       | 6                           | VCCA-1   | Reference voltage input.                 |

| COMP                  | 7                       | 7                           | 0.1μF    | Compensation capacitor.                  |

| Data Input            |                         |                             | •        |                                          |

| D <sub>1</sub> (MSB)  | 19                      | 23                          | TTL      | Most Significant Bit Input.              |

| D2-D9                 | 20–27                   | 24–31                       | TTL      |                                          |

| D <sub>10</sub> (LSB) | 28                      | 32                          | TTL      | Least Significant Bit Input.             |

| INVERT                | 5                       | 5                           | TTL      | Invert D <sub>1</sub> –D <sub>10</sub> . |

| SYNC                  | 4                       | 3                           | TTL      | SYNC input.                              |

| BLANK                 | 3                       | 2                           | TTL      | BLANK input.                             |

| Clock                 | <u> </u>                |                             | •        |                                          |

| CONV                  | 18                      | 22                          | TTL      | Clock input.                             |

| Output                | <del>.</del>            |                             | •        |                                          |

| Vout                  | 8                       | 8                           | +4 to +5 | Analog output.                           |

| No Connect            | <del>_</del>            |                             | •        |                                          |

| NC                    | 1, 2, 11, 13, 14,<br>16 | 4, 11, 12,<br>14–16, 18, 21 | Open     | Not connected.                           |

**Figure 1. Video Output Waveforms**

# **Absolute Maximum Ratings<sup>1</sup>**

| Туре            | Parameter                                       | Min. | Max.     | Unit |  |  |  |

|-----------------|-------------------------------------------------|------|----------|------|--|--|--|

| Supply Voltages | VCCA (measured to AGND)                         | -0.5 | +7.0     | V    |  |  |  |

|                 | VCCD (measured to DGND)                         | -0.5 | +7.0     | V    |  |  |  |

|                 | VCCA (measured to VCCD)                         | -0.5 | +0.5     | V    |  |  |  |

|                 | AGND (measured to DGND)                         | -0.5 | +0.5     | V    |  |  |  |

| Inputs          | CONV, D1−10, SYNC, BLANK, INVERT                |      |          |      |  |  |  |

|                 | Applied voltage (measured to DGND) <sup>2</sup> | -0 5 | +7.0     | V    |  |  |  |

|                 | Externally forced current <sup>3</sup>          | -10  | +10      | mA   |  |  |  |

|                 | VREF                                            |      |          |      |  |  |  |

|                 | Applied voltage (measured to AGND) <sup>2</sup> | -0 5 | VCCA + 2 | V    |  |  |  |

|                 | Externally forced current <sup>3</sup>          | -10  | +10      | mA   |  |  |  |

| Output          | Vout                                            |      |          |      |  |  |  |

|                 | Applied voltage (measured to AGND) <sup>2</sup> | +3.0 | 7.0      | V    |  |  |  |

|                 | Externally forced current <sup>3</sup>          | -20  | +20      | mA   |  |  |  |

| Temperature     | R6 Package                                      |      |          |      |  |  |  |

|                 | Operating, ambient                              | -25  | +90      | °C   |  |  |  |

|                 | Junction                                        |      | +140     | °C   |  |  |  |

|                 | B6 Package                                      |      |          |      |  |  |  |

|                 | Operating, ambient                              | -60  | +150     | °C   |  |  |  |

|                 | Junction                                        |      | +200     | °C   |  |  |  |

|                 | Lead, soldering (10 seconds)                    |      | +300     | °C   |  |  |  |

|                 | Storage                                         | -65  | +150     | °C   |  |  |  |

- Absolute maximum ratings are limiting values applied to individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied. Device performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

# **Operating Conditions**

| Parameter | Description                       | Min.     | Nom.     | Max.     | Unit |

|-----------|-----------------------------------|----------|----------|----------|------|

| VCCA      | Analog Power Supply Voltage       | 4.75     | 5.00     | 5.25     | V    |

| VDDC      | Digital Power Supply Voltage      | 4.75     | 5.00     | 5.25     | V    |

| VCCA-VCCD | Power Supply Voltage Differential | -0.1     | 0.0      | 0.1      | V    |

| AGND-DGND | Ground Voltage Differential       | -0.1     | 0.0      | 0.1      | V    |

| VREF      | Reference Voltage                 | VCCA-1.5 | VCCA-1.0 | VCCA-0.5 | V    |

| Cc        | Compensation Capacitor            | 0.01     | 0.1      |          | μF   |

| VIL       | Input Voltage, Logic LOW          |          |          | 0.8      | V    |

| VIH       | Input Voltage, Logic HIGH         | 2.0      |          |          | V    |

| ts        | Input Data Setup Time             | 20       |          |          | ns   |

| tH        | Input Data Hold Time              | 2        |          |          | ns   |

| tpwL      | CONV Pulse Width, LOW             | 10       |          |          | ns   |

| tPWH      | CONV Pulse Width, HIGH            | 10       |          |          | ns   |

| TA        | Temperature Range, Still Air      | 0        |          | 70       | °C   |

# **DC Electrical Characteristics**

| Symbol | Parameter                 | Conditions                                          | Min.  | Тур. | Max.  | Unit |

|--------|---------------------------|-----------------------------------------------------|-------|------|-------|------|

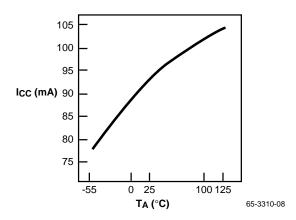

| Icc    | Supply Current            | VCCD = VCCA = Maximum                               |       | 70   | 115   | mA   |

| CIN    | Input Capacitance         | CONV, D <sub>1-10</sub> , SYNC, BLANK, INVERT, VREF |       | 5    | 10    | pF   |

| I∣L    | Input Current, Logic LOW  | VCCD = Max., VI = 0.4V                              |       | -200 | -400  | μΑ   |

| lін    | Input Current, Logic HIGH | VDDC = Max., VI = 2.4V                              |       | 10   | 100   | pА   |

| Ro     | Output Resistance         | Vout to Vcca, T <sub>A</sub> = +25°C                | 80    | 90   | 100   | Ω    |

| Co     | Output Capacitance        | Vout Terminal                                       |       |      | 20    | pF   |

| Voc    | Output Compliance         | Referred to VCCA                                    | -1.5  | 0    | +0.4  | V    |

| VFS    | Full-Scale Output         | Referred to VCCA, VREF = Nominal                    | -0.95 | -1.0 | -1.05 | V    |

| VBLANK | Blank Output Voltage      | Referred to VFS, VREF = Nominal                     | -71   | -81  | -91   | mV   |

| VSYNC  | Sync Output Voltage       | Referred to VBLANK, VREF = Nominal                  | -380  | -433 | -480  | mV   |

# **AC Electrical Characteristics**

| Symbol | Parameter                               | Conditions               | Min. | Тур. | Max. | Unit   |

|--------|-----------------------------------------|--------------------------|------|------|------|--------|

| fs     | Maximum Clock Rate                      | VCCA, VCCD = Minimum     | 40   |      |      | MHz    |

| tco    | Clock to Output Delay <sup>1, 2</sup>   | VCCA, VDDC = Minimum     |      | 8    | 15   | ns     |

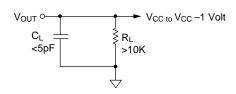

| tR     | Output Risetime <sup>1, 2</sup>         | 90% to 10% of Full Scale |      | 5    | 10   | ns     |

| tF     | Output Falltime <sup>1, 2</sup>         | 10 to 90% of Full Scale  |      | 5    | 10   | ns     |

| tSET   | Output Settling Time <sup>1, 2, 3</sup> | to 1%                    |      | 10   | 18   | ns     |

|        |                                         | to +1 LSB                |      | 25   | 40   | ns     |

| GA     | Peak Glitch Area <sup>2,3</sup>         |                          |      | 50   |      | pV-sec |

- 1. See Timing Diagram.

- 2. Standard Test Load, Figure 4.

- 3. Worst-case transition.

# **System Performance Characteristics**

| Symbol | Parameter                    | Conditions                         | Min. | Тур. | Max. | Unit    |

|--------|------------------------------|------------------------------------|------|------|------|---------|

| ELD    | Differential Linearity Error | VCCA, VCCD, VREF = Nom.            |      | ±0.5 | ±1.0 | LSB     |

| ELI    | Integral Linearity Error     | VCCA, VCCD, VREF = Nom             |      | ±0.5 | ±1.0 | LSB     |

| Eg     | Absolute Gain Error          | VCCA, VCCD, VREF = Nom.            |      | ±1   | ±5   | %       |

| TCEG   | Gain Error Tempco            | VCCA, VCCD, VREF = Nom.            |      | ±30  |      | ppm/°C  |

| VOF    | Output Offset Voltage        | VCCA, VCCD = Max.,<br>D1-10 = HIGH |      | -10  | -25  | mV      |

| TCOF   | Offset Tempco                | VCCA, VCCD = Max.,<br>D1-10 = HIGH |      | -50  |      | μV/°C   |

| IREF   | VREF Input Bias Current      |                                    |      | 1    | 5    | μΑ      |

| DP     | Differential Phase           | fs = 4 x NTSC Subcarrier           |      | 0.2  |      | Degrees |

| DG     | Differential Gain            | fs = 4 x NTSC Subcarrier           |      | 0.3  |      | %       |

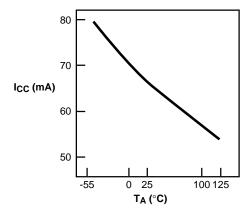

# **Performance Curves**

Figure 2. Power Supply vs. Temperature

Figure 3. ROUT vs. Temperature

# **Input Coding Table**

| D1D10<br>(MSB LSB) | BLANK | SYNC | INVERT = LOW<br>Vout w/r Vcca | V <sub>OUT</sub> w/r<br>AGND | INVERT = HIGH<br>Vout w/r Vcca | V <sub>OUT</sub> w/r<br>AGND |

|--------------------|-------|------|-------------------------------|------------------------------|--------------------------------|------------------------------|

| 11 1111 1111       | 0     | 0    | 0.000                         | 5.000                        | -1.000                         | 4.000                        |

| 11 1111 1110       | 0     | 0    | -0.001                        | 4.999                        | -0.999                         | 4.001                        |

| 11 1111 1101       | 0     | 0    | -0.002                        | 4.998                        | -0.998                         | 4.002                        |

| :                  | :     | :    | :                             | :                            | :                              | :                            |

| 10 0000 0000       | 0     | 0    | -0.500                        | 4.500                        | -0.501                         | 4.499                        |

| 01 1111 1111       | 0     | 0    | -0.501                        | 4.499                        | -0.500                         | 4.500                        |

| :                  | :     | :    | :                             | :                            | :                              | :                            |

| 00 0000 0010       | 0     | 0    | -0.998                        | 4.002                        | -0.002                         | 4.998                        |

| 00 0000 0001       | 0     | 0    | -0.999                        | 4.001                        | -0.001                         | 4.999                        |

| 00 0000 0000       | 0     | 0    | -1.000                        | 4.000                        | 0.000                          | 5.000                        |

| xx xxxx xxxx       | 1     | 0    | -1.081                        | 3.919                        | -1.081                         | 3.919                        |

| xx xxxx xxxx       | х     | 1    | -1.514                        | 3.486                        | -1.514                         | 3.486                        |

#### Note:

1.  $V_{REF} = V_{CCA} - 1.000 \text{ volts}$ ,  $V_{CCA} = 5.0 \text{ volts}$ , no external.

# **Timing Diagrams**

Figure 4. Timing Diagram

Figure 5. Equivalent Reference and Output Circuit

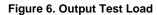

Figure 7. Output Load for DP and DG

### **Application Notes**

Since the internal reference and output circuits of the TDC3310 are referred to the power supply, VCC, the external voltage reference shown in the Typical Interface Circuit is also referred to VCC. A simple 1.2 volt Bandgap reference diode is voltage-divided to provide 1.0 volts between the VREF and VCC inputs. The output of the TDC3310 is AC coupled into a  $75\Omega$  resistor which divides the output video level by a factor of two. The video amplifier gain is +2, restoring the 1 Vp-p video level and referring the video signal to AGND. It is important to ensure the power supply for the TDC3310 is well-regulated and free of high-frequency noise. Careful power supply decoupling will ensure the highest quality video signals at the output of the circuit.

### Grounding

The TDC3310 has separate analog and digital circuits. To keep digital system noise from the D/A converter, it is recommended that power supply voltages ( $V_{DDD}$  and  $V_{DDA}$ ) come from the same source and ground connections (DGND and AGND) be made to the analog ground plane. Power supply pins should be individually decoupled at the pin.

The digital circuitry that gets its input from the TMC1173 should be referred on the system digital ground plane.

### **Printed Circuit Board Layout**

Designing with high-performance mixed-signal circuits demands printed circuits with ground planes. Wire-wrap is not an option—even for breadboarding. Overall system performance is strongly influenced by the board layout. Capacitive coupling from digital to analog circuits may result in poor A/D conversion. Consider the following suggestions when doing the layout.

- Keep the critical analog traces (VIN, RT, RB, VR+, VR-)

as short as possible and as far as possible away from all

digital signals. The TMC1173 should be located near

the board edge, close to the analog output connectors.

- 2. The power plane for the TMC1173 should be separate from that which supplies the rest of the digital circuitry. A single power plane should be used for all of the VDD pins. If the power supply for the TMC1173 is the same as that of the system's digital circuitry, power to the TMC1173 should be decoupled with ferrite beads and 0.1 μF capacitors to reduce noise.

- The ground plane should be solid, not crosshatched. Connections to the ground plane should have very short leads.

- 4. Decoupling capacitors should be applied liberally to VDD pins. Remember that not all power supply pins are created equal. They typically supply adjacent circuitry on the device, which generate varying amounts of noise. For best results, use 0.1 μF ceramic capacitors. Lead lengths should be minimized. Ceramic chip capacitors are the best choice.

- 5. If the digital power supply has a dedicated power plane layer, it should not overlap the TMC1173, the voltage reference or the analog inputs. Capacitive coupling of digital power supply noise from this layer to the TMC1173 and its related analog circuitry can have an adverse effect on performance.

- CONV should be handled carefully. Jitter and noise on this clock may degrade performance. Terminate the clock line carefully to eliminate overshoot and ringing.

Figure 8. Typical Interface Circuit

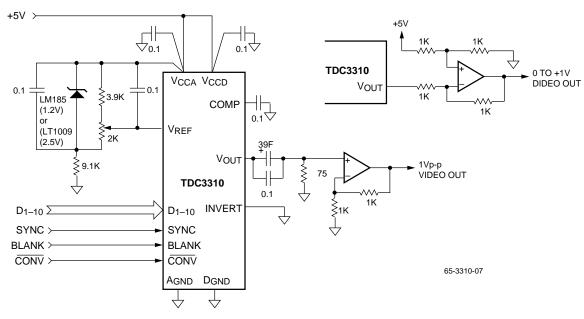

## **Mechanical Dimensions**

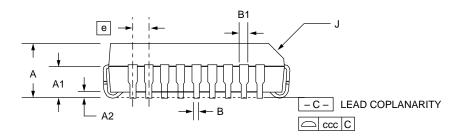

# 32 Lead Plastic Chip Carrier

| Symbol | Inches   |          | Millin | Notes |       |

|--------|----------|----------|--------|-------|-------|

| Symbol | Min.     | Max.     | Min.   | Max.  | Notes |

| Α      | .126     | .146     | 3.20   | 3.71  |       |

| A1     | .054     | .074     | 1.37   | 1.88  |       |

| A2     | .020     | _        | .51    | _     |       |

| В      | .013     | .021     | .33    | .53   |       |

| B1     | .026     | .032     | .66    | .81   |       |

| D      | .480     | .500     | 12.19  | 12.70 |       |

| Е      | .580     | .600     | 14.73  | 15.24 |       |

| D1     | .438     | .458     | 11.12  | 11.63 | 3     |

| E1     | .538     | .558     | 13.67  | 14.17 | 3     |

| D3     | .300     | .300 BSC |        | BSC   |       |

| E3     | .500     | BSC      | 12.70  | BSC   |       |

| е      | .050     | BSC      | 1.27   | BSC   |       |

| J      | .042     | .056     | 1.07   | 1.42  | 2     |

| ND/NE  | 7.       | /9       | 7.     | /9    |       |

| N      | 3        | 2        | 32     |       |       |

| CCC    | <u> </u> | .004     | _      | 0.10  |       |

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982

- 2. Corner and edge chamfer (J) =  $45^{\circ}$

- 3. Dimension D1 and E1 do not include mold protrusion. Allowable protrusion is .101 inch (.245mm)

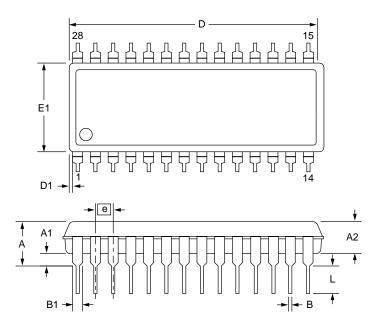

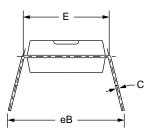

# **Mechanical Dimensions** (continued)

# 28 Lead Plastic DIP - .600" Body Width

| Cumbal | Inches |       | Millim   | Notes |       |

|--------|--------|-------|----------|-------|-------|

| Symbol | Min.   | Max.  | Min.     | Max.  | Notes |

| Α      | _      | .250  | _        | 6.35  |       |

| A1     | .015   |       | .38      | _     |       |

| A2     | .125   | .195  | 3.18     | 4.95  |       |

| В      | .014   | .022  | .36      | .56   |       |

| B1     | .030   | .070  | .76      | 1.78  |       |

| С      | .008   | .015  | .20      | .38   | 4     |

| D      | 1.380  | 1.565 | 35.05    | 39.75 | 2     |

| D1     | .005   | _     | .13      | _     |       |

| Е      | .600   | .625  | 15.24    | 15.88 |       |

| E1     | .485   | .580  | 12.32    | 14.73 | 2     |

| е      | .100   | BSC   | 2.54 BSC |       |       |

| eВ     | _      | .700  | _        | 17.78 |       |

| L      | .115   | .200  | 2.92     | 5.08  |       |

| N      | 2      | 8     | 2        | 8     | 5     |

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 2. "D" and "E1" do not include mold flashing. Mold flash or protrusions shall not exceed .010 inch (0.25mm).

- 3. Terminal numbers are shown for reference only.

- 4. "C" dimension does not include solder finish thickness.

- 5. Symbol "N" is the maximum number of terminals.

# **Ordering Information**

| Product<br>Number | Linearity<br>Error (LSB) | Temperature<br>Range                | Screening  | Package             | Package<br>Marking |

|-------------------|--------------------------|-------------------------------------|------------|---------------------|--------------------|

| TDC3310N6C        | ±1.0                     | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | Commercial | 28-pin Plastic DIP  | 3310N6C            |

| TDC3310R6C        | ±1.0                     | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | Commercial | 32-Lead J-Lead PLCC | 3310R6C            |

| TMC1175E1C        | 30                       | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | Commercial | Eurocard PC Board   | TMC1175E1C         |

The information contained in this data sheet has been carefully compiled; however, it shall not by implication or otherwise become part of the terms and conditions of any subsequent sale. Raytheon's liability shall be determined solely by its standard terms and conditions of sale. No representation as to application or use or that the circuits are either licensed or free from patent infringement is intended or implied. Raytheon reserves the right to change the circuitry and any other data at any time without notice and assumes no liability for errors.

### LIFE SUPPORT POLICY:

Raytheon's products are not designed for use in life support applications, wherein a failure or malfunction of the component can reasonably be expected to result in personal injury. The user of Raytheon components in life support applications assumes all risk of such use and indemnifies Raytheon Company against all damages.

Raytheon Electronics Semiconductor Division 5580 Morehouse Drive San Diego, CA 92121 619 457 1000 800 722 7074 Fax 619 455 6314 applications@lj.sd.ray.com